# EE 435

## Lecture 32

- Parasitic Capacitances

- String DACs

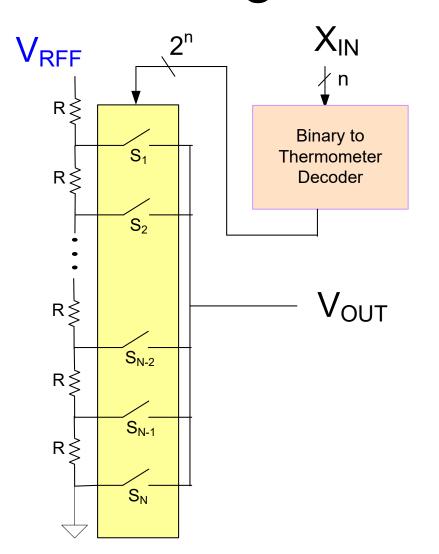

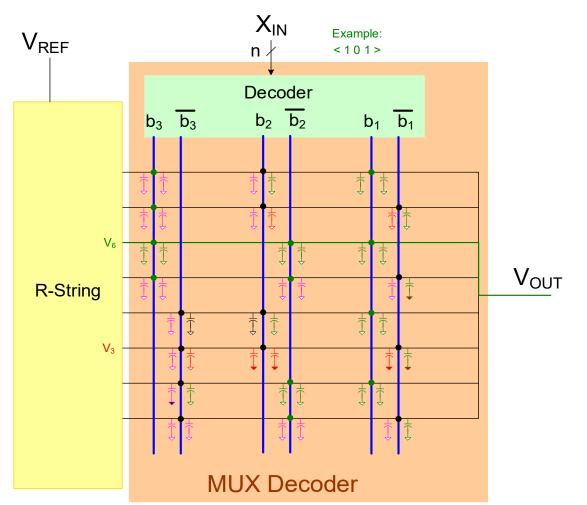

### Review from Last Lecture R-String DAC

**Basic R-String DAC including Logic to Control Switches**

### Review from Last Lecture Nonideal Effects of Concern

- Matching

- Parasitic Capacitances (including Charge injection)

- Loading

- Nonlinearities

- Previous code dependence

- Code-dependent settling

- Interconnect resistors

- Noise

- Slow and plagued by jitter

- Temperature Effects

- Aging

- Package stress

#### **Review from Last Lecture**

# Data Converter Design Strategies

- There are many different DAC and ADC architectures that have been proposed and that are in widespread use today

- Almost all work perfectly if all components are ideal

- Most data converter design work involves identifying the contributors to nonideal performance and finding work-arounds to these problems

- Some architectures are more difficult to find work-arounds than others

- All contributors to nonidealities that are problematic at a given resolution of speed level must be identified and mitigated

- The effects of not identifying nonidealities generally fall into one of two categories

- Matching-critical nonidealities (degrade yield)

- Component nonlinearities (degrade performance even if desired matching is present)

Review from Last Lecture

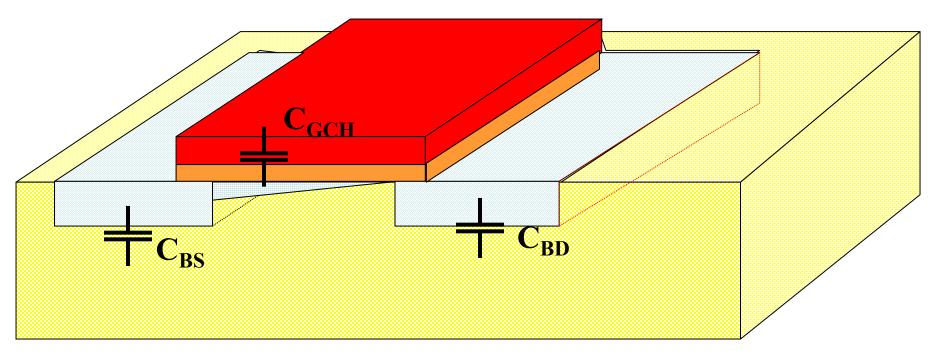

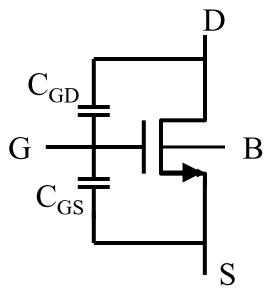

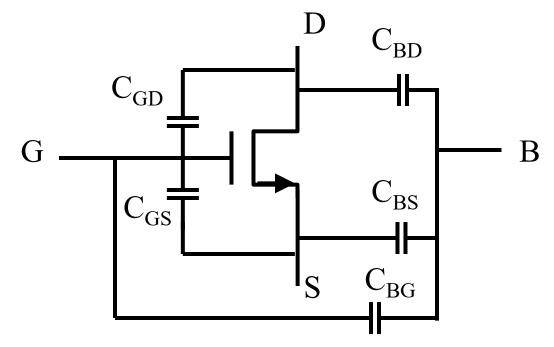

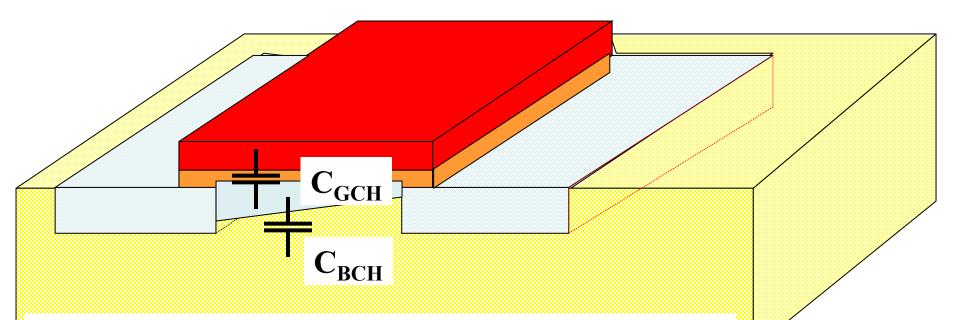

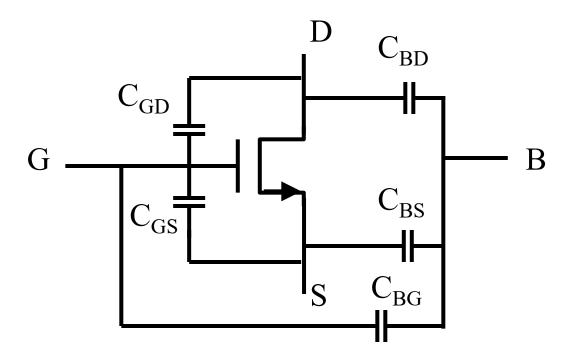

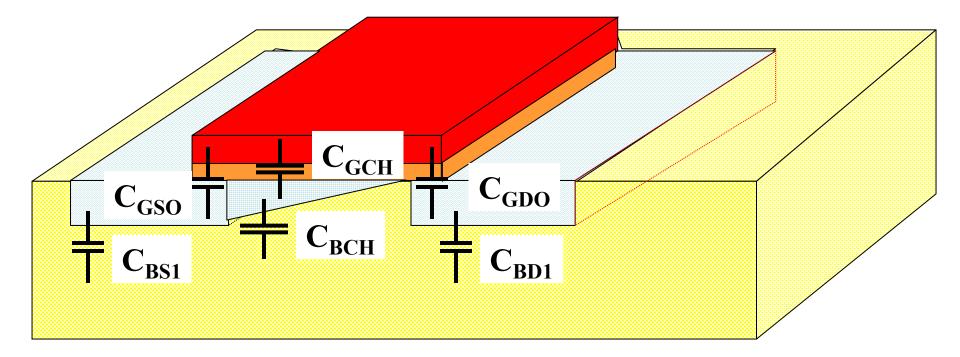

# Parasitic Capacitors in MOSFET

(initially assume saturation and consider two: Gate-channel and diffusion)

- Diffusion capacitances nonlinear (dependent upon voltage)

- Many more actually present

- Operating region may affect parasitics

**Review from Last Lecture**

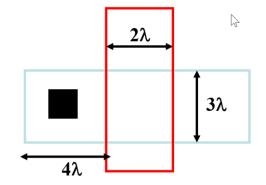

# Size of Capacitances

Gate-Channel Capacitance =  $6\lambda^2 \ge 2.47 \text{fF}/\mu^2 = 1.33 \text{fF}$

#### Source Diffusion-Substrate Capacitance = $12\lambda^2 \times .424 fF/\mu^2 + 14\lambda \times .315 fF/\mu =$ .46 fF + 1.32 fF = 1.78 fF

Note Sidewall Capacitance larger than Bottom Capacitance

Are these negligible?

#### Reminder !!

#### Identifying Problems/Challenges and Clever/Viable Solutions

- Many problems occur repeatedly so should recognize when they occur

- Identify clever solutions to basic problems they often are useful in many applications

- Don't make the same mistake twice !

The problem:

The perceived solution:

The practical or clever solution:

The List ! The List Keeper !

# **Types of Capacitors**

- 1. Fixed Capacitors

- a. Fixed Geometry

- b. Junction

- 2. Operating Region Dependent

- a. Fixed Geometry

- b. Junction

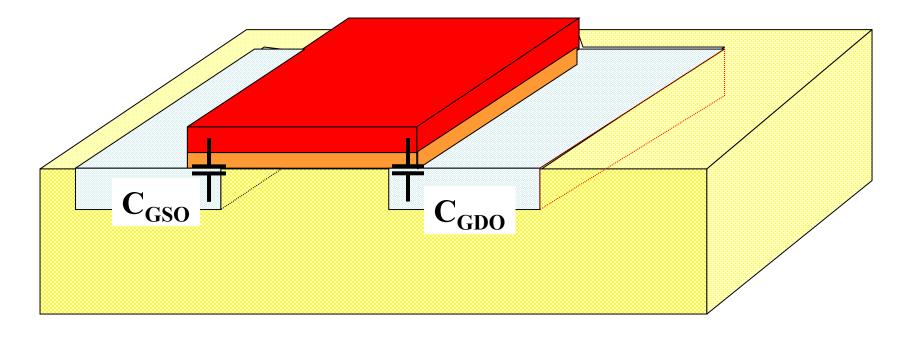

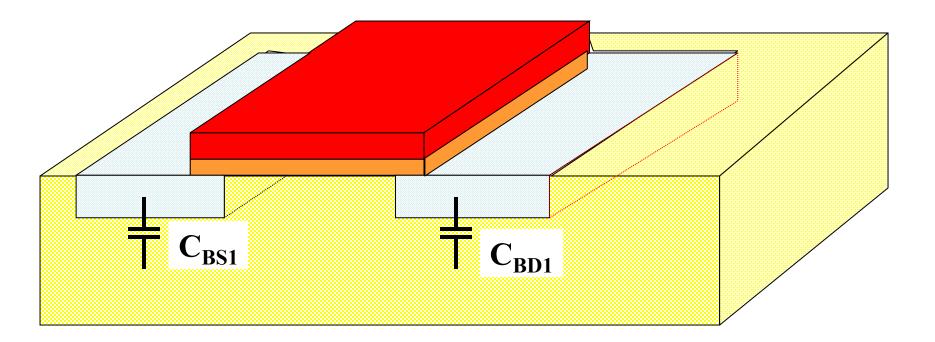

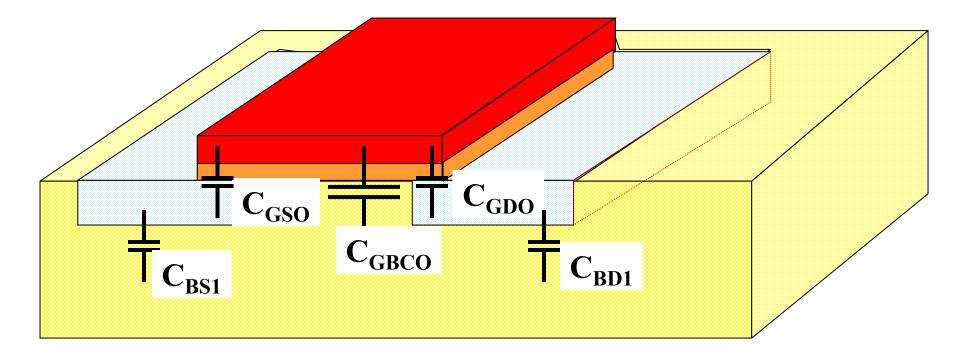

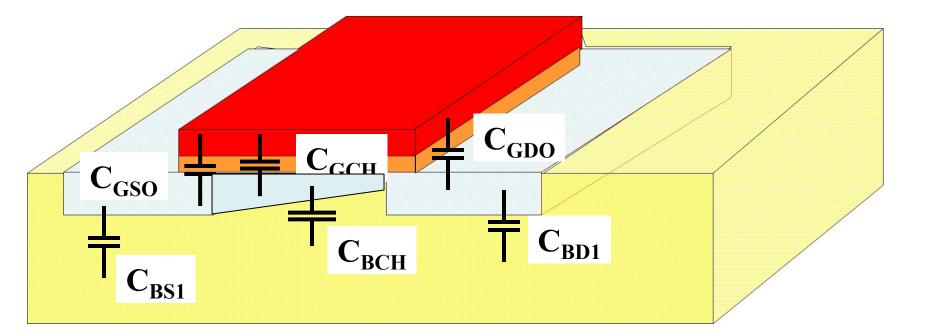

# Parasitic Capacitors in MOSFET Fixed Capacitors

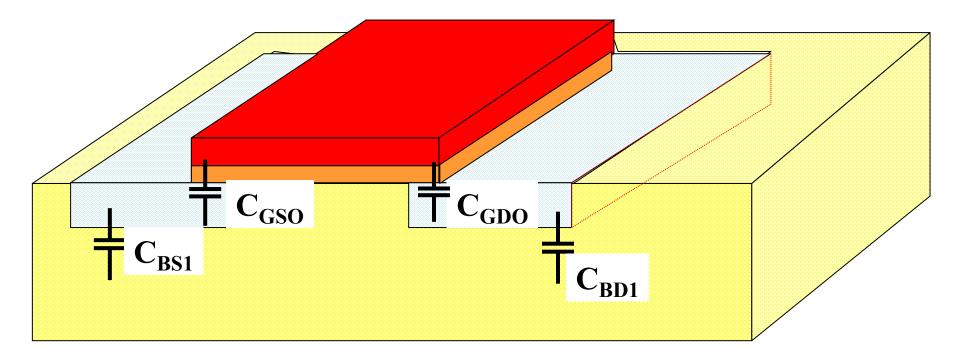

# Parasitic Capacitors in MOSFET Fixed Capacitors

Overlap Capacitors: C<sub>GDO</sub>, C<sub>GSO</sub>

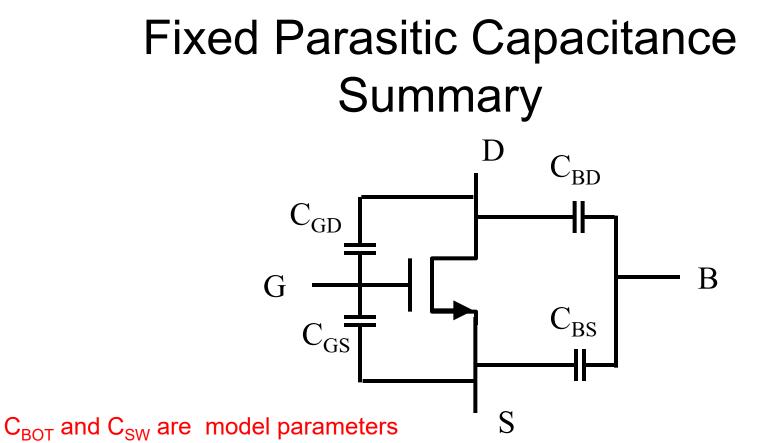

# Fixed Parasitic Capacitance Summary

|                 | Cutoff             | Ohmic              | Saturation         |

|-----------------|--------------------|--------------------|--------------------|

| C <sub>GS</sub> | CoxWL <sub>D</sub> | CoxWL <sub>D</sub> | CoxWL <sub>D</sub> |

|                 | CoxWL <sub>D</sub> | CoxWL <sub>D</sub> | CoxWL <sub>D</sub> |

$L_{\rm D}$  is a model parameter

## Parasitic Capacitors in MOSFET Fixed Capacitors

Junction Capacitors: C<sub>BS1</sub>, C<sub>BD1</sub>

## Parasitic Capacitors in MOSFET Fixed Capacitors

Overlap Capacitors:  $C_{GDO}$ ,  $C_{GSO}$ Junction Capacitors:  $C_{BS1}$ ,  $C_{BD1}$

|                 | Cutoff                             | Ohmic                                  | Saturation                         |

|-----------------|------------------------------------|----------------------------------------|------------------------------------|

| C <sub>GS</sub> | CoxWL <sub>D</sub>                 | CoxWL <sub>D</sub>                     | CoxWL <sub>D</sub>                 |

|                 | CoxWL <sub>D</sub>                 | CoxWL <sub>D</sub>                     | CoxWL <sub>D</sub>                 |

| C <sub>BG</sub> |                                    |                                        |                                    |

| C <sub>BS</sub> | $C_{BS1} = C_{BOT}A_S + C_{SW}P_S$ | $C_{BS1} = C_{BOT}A_S + C_{SW}P_S$     | $C_{BS1} = C_{BOT}A_S + C_{SW}P_S$ |

| C <sub>BD</sub> | $C_{BD1} = C_{BOT}A_D + C_{SW}P_D$ | $C_{BD1} = C_{BOT}A_{D} + C_{SW}P_{D}$ | $C_{BD1} = C_{BOT}A_D + C_{SW}P_D$ |

# Parasitic Capacitors in MOSFET Operation Region Dependent

### Parasitic Capacitors in MOSFET Operation Region Dependent -- Cutoff

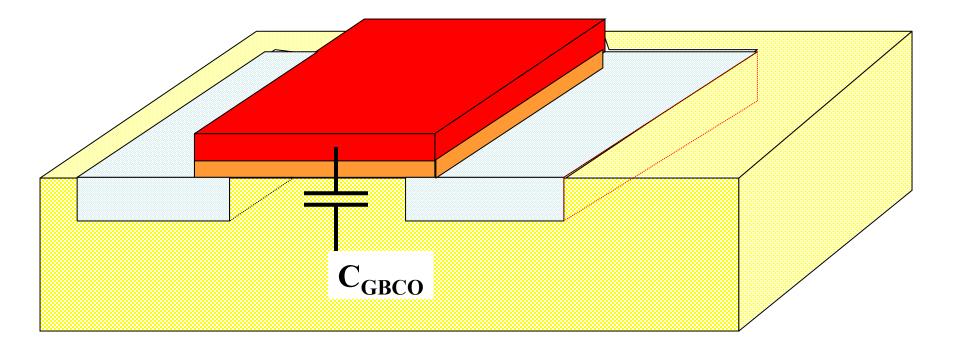

#### **Cutoff Capacitor: C**<sub>GBCO</sub>

## Parasitic Capacitors in MOSFET Operation Region Dependent -- Cutoff

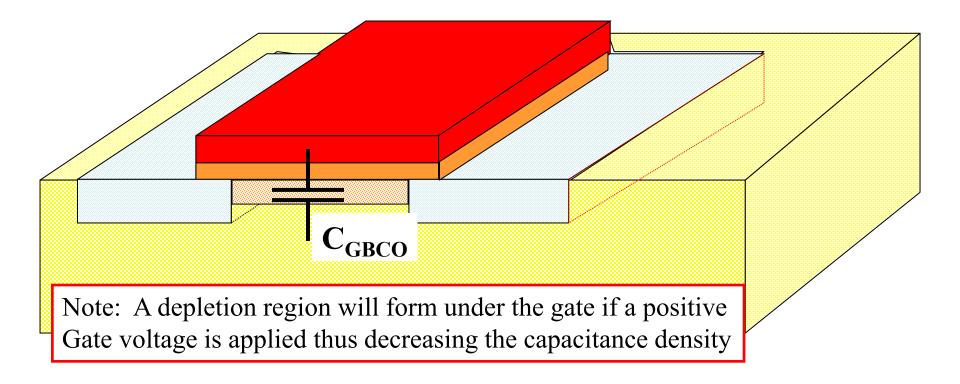

#### **Cutoff Capacitor: C**<sub>GBCO</sub>

#### Parasitic Capacitors in MOSFET Operation Region Dependent and Fixed -- Cutoff

Overlap Capacitors:  $C_{GDO}$ ,  $C_{GSO}$ Junction Capacitors:  $C_{BS1}$ ,  $C_{BD1}$ **Cutoff Capacitor:**  $C_{GBCO}$

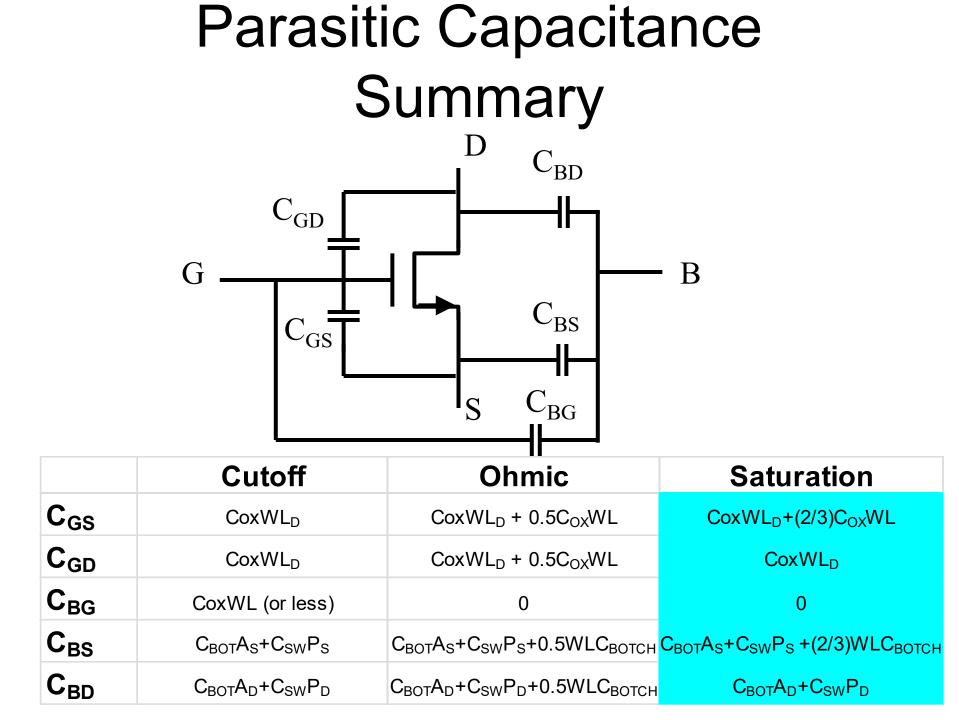

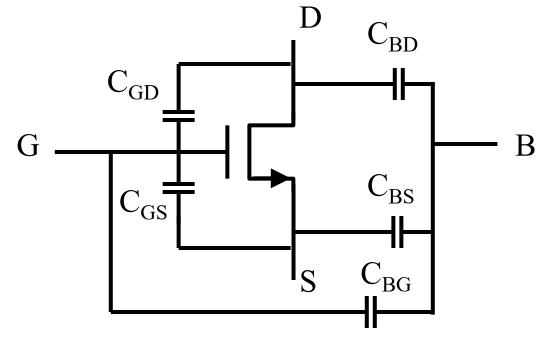

## Parasitic Capacitance Summary

|                 | Cutoff                                                          | Ohmic | Saturation |

|-----------------|-----------------------------------------------------------------|-------|------------|

| C <sub>GS</sub> | CoxWL <sub>D</sub>                                              |       |            |

|                 | CoxWL <sub>D</sub>                                              |       |            |

| C <sub>BG</sub> | CoxWL (or less)                                                 |       |            |

| C <sub>BS</sub> | C <sub>BOT</sub> A <sub>S</sub> +C <sub>SW</sub> P <sub>S</sub> |       |            |

| C <sub>BD</sub> | C <sub>BOT</sub> A <sub>D</sub> +C <sub>SW</sub> P <sub>D</sub> | -     |            |

## Parasitic Capacitors in MOSFET Operation Region Dependent -- Ohmic

Note: The Channel is not a node in the lumped device model so can not directly include this distributed capacitance in existing models

Note: The distributed channel capacitance is usually lumped and split evenly between the source and drain nodes

### Ohmic Capacitor: $C_{GCH}$ , $C_{BCH}$

### Parasitic Capacitors in MOSFET Operation Region Dependent and Fixed -- Ohmic

Overlap Capacitors:  $C_{GDO}$ ,  $C_{GSO}$ Junction Capacitors:  $C_{BS1}$ ,  $C_{BD1}$ **Ohmic Capacitor:**  $C_{GCH}$ ,  $C_{BCH}$

### Parasitic Capacitance Summary

|                 | Cutoff                                                          | Ohmic                              | Saturation |

|-----------------|-----------------------------------------------------------------|------------------------------------|------------|

| C <sub>GS</sub> | CoxWL <sub>D</sub>                                              | CoxWL <sub>D</sub>                 |            |

|                 | CoxWL <sub>D</sub>                                              | CoxWL <sub>D</sub>                 |            |

| C <sub>BG</sub> | CoxWL (or less)                                                 |                                    |            |

| C <sub>BS</sub> | C <sub>BOT</sub> A <sub>S</sub> +C <sub>SW</sub> P <sub>S</sub> | $C_{BS1} = C_{BOT}A_S + C_{SW}P_S$ |            |

| C <sub>BD</sub> | C <sub>BOT</sub> A <sub>D</sub> +C <sub>SW</sub> P <sub>D</sub> | $C_{BD1} = C_{BOT}A_D + C_{SW}P_D$ |            |

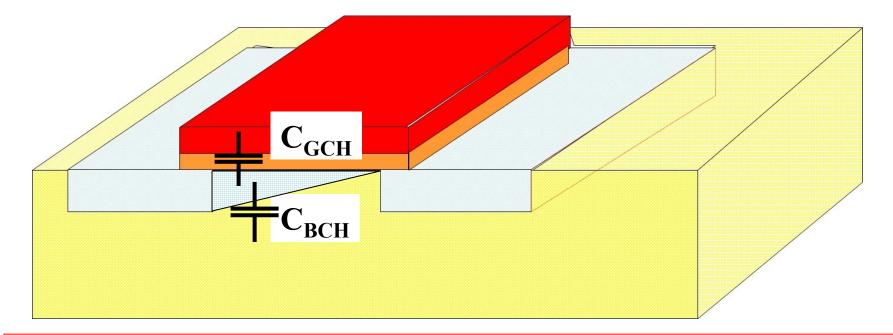

### Parasitic Capacitors in MOSFET Operation Region Dependent -- Saturation

Note: Since the channel is an extension of the source when in saturation, the distributed capacitors to the channel are generally lumped to the source node

### Saturation Capacitors: $C_{GCH}$ , $C_{BCH}$

### Parasitic Capacitors in MOSFET Operation Region Dependent and Fixed --Saturation

Overlap Capacitors:  $C_{GDO}$ ,  $C_{GSO}$ Junction Capacitors:  $C_{BS1}$ ,  $C_{BD1}$ **Saturation Capacitors:**  $C_{GCH}$ ,  $C_{BCH}$

## Parasitic Capacitance Summary

|                 | Cutoff                     | Ohmic                                                                                    | Saturation                                                                                 |

|-----------------|----------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| C <sub>GS</sub> | CoxWL <sub>D</sub>         | $CoxWL_{D} + 0.5C_{OX}WL$                                                                | CoxWL <sub>D</sub> +(2/3)C <sub>OX</sub> WL                                                |

|                 | CoxWL <sub>D</sub>         | $CoxWL_{D} + 0.5C_{OX}WL$                                                                | CoxWL <sub>D</sub>                                                                         |

| C <sub>BG</sub> | CoxWL (or less)            | 0                                                                                        | 0                                                                                          |

| C <sub>BS</sub> | $C_{BOT}A_{S}+C_{SW}P_{S}$ | C <sub>BOT</sub> A <sub>S</sub> +C <sub>SW</sub> P <sub>S</sub> +0.5WLC <sub>BOTCH</sub> | C <sub>BOT</sub> A <sub>S</sub> +C <sub>SW</sub> P <sub>S</sub> +(2/3)WLC <sub>BOTCH</sub> |

| C <sub>BD</sub> | $C_{BOT}A_D + C_{SW}P_D$   | C <sub>BOT</sub> A <sub>D</sub> +C <sub>SW</sub> P <sub>D</sub> +0.5WLC <sub>BOTCH</sub> | $C_{BOT}A_{D}+C_{SW}P_{D}$                                                                 |

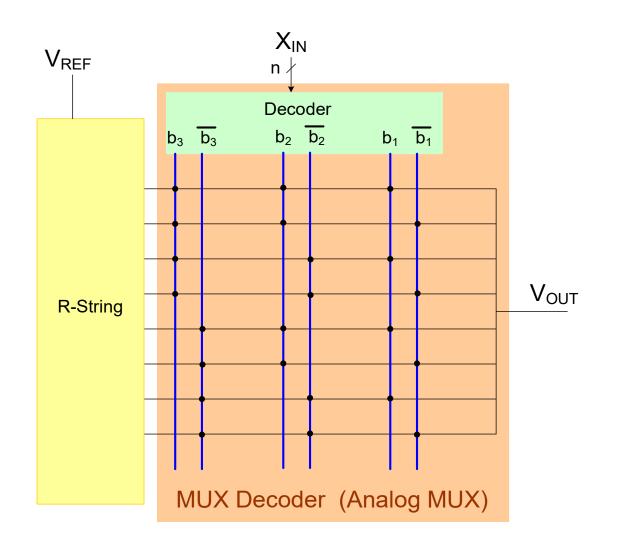

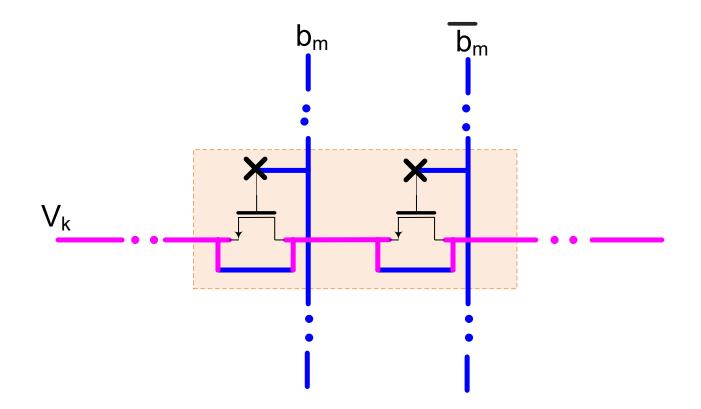

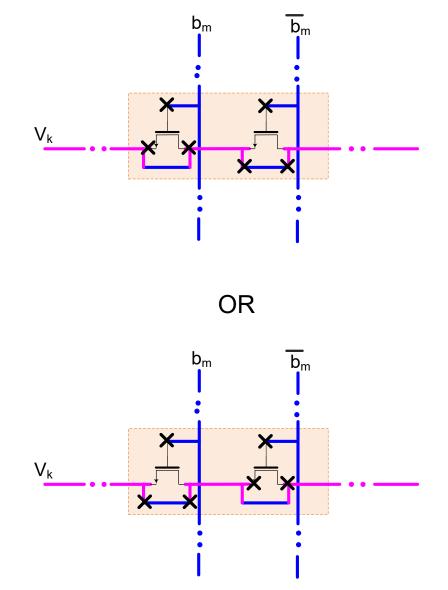

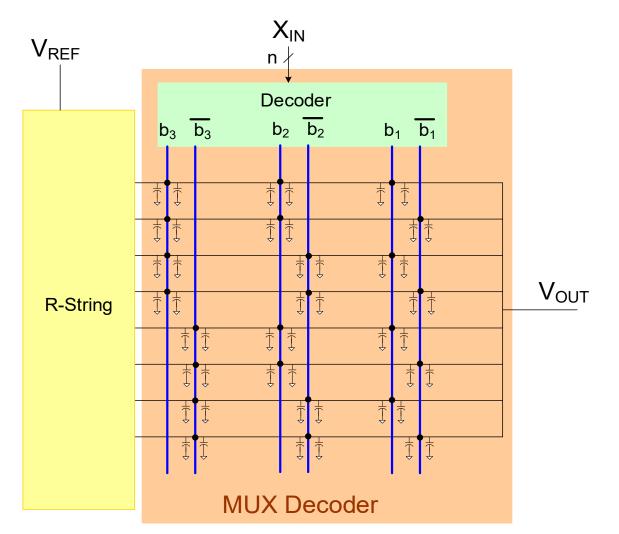

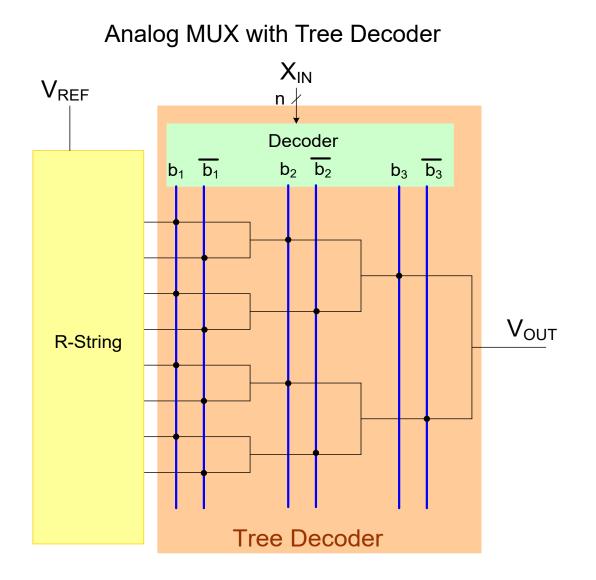

Tree-Decoder Layout/Architecture

Each intersection is a reserved site for a switch

#### **Uncontacted Row-Column Structure**

### **Row-Column Structure with Contacts Added**

Programmed entirely with the contact mask

#### Parasitic Capacitances in MUX Decoder

(for convenience have not shown non-contacted transistor effects)

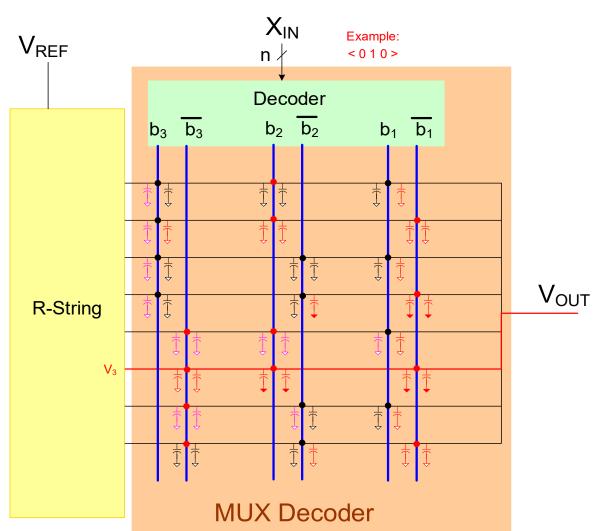

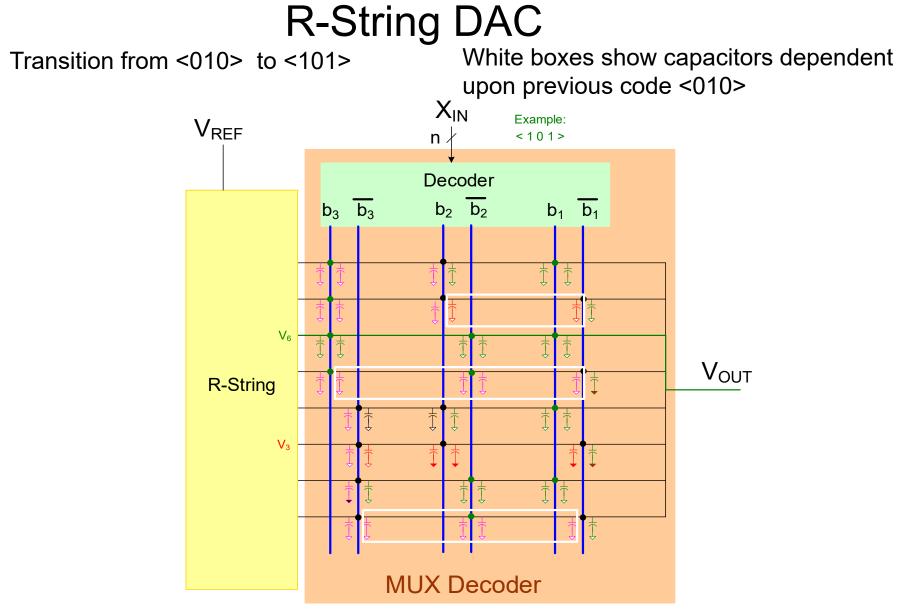

#### **Previous-Code Dependent Settling**

Assume all C's initially with 0V Red denotes  $V_3$ , black denotes 0V, Purple some other voltage

Transition from <010> to <101>

#### **Previous-Code Dependent Settling**

Assume all C's initially with 0V

Red denotes  $V_3$ , green denotes  $V_6$ , black denotes 0V, Purple some other voltage

#### **Previous-Code Dependent Settling**

Assume all C's initially with 0V

Red denotes  $V_3$ , green denotes  $V_6$ , black denotes 0V, Purple some other voltage

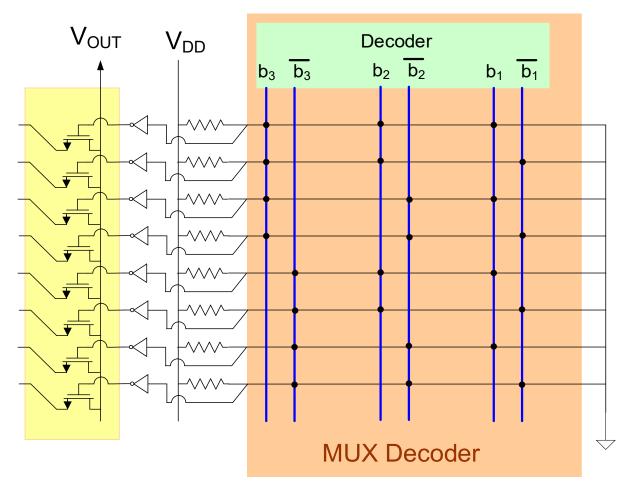

#### **Tree-Decoder in Digital Domain**

Single transistor used at each marked intersection to form PTL -AND gates

Do the resistors that form part of PTL dissipate any substantial power? No because only one will be conducting for any DAC output

#### DAC8560 16-Bit, Ultra-Low Glitch, Voltage Output Digital-to-Analog Converter With 2.5-V, 2-ppm/°C Internal Reference

#### 1 Features

- Relative Accuracy: 4 LSB

- Glitch Energy: 0.15 nV-s

- MicroPower Operation: 510 μA at 2.7 V

- Internal Reference:

- 2.5-V Reference Voltage (Enabled by Default)

- 0.02% Initial Accuracy

- 2-ppm/°C Temperature Drift (Typical)

- 5-ppm/°C Temperature Drift (Maximum)

- 20-mA Sink/Source Capability

- Power-On Reset to Zero

- Power Supply: 2.7 V to 5.5 V

- 16-Bit Monotonic Over Temperature Range

- Settling Time: 10 μs to ±0.003% FSR

- Low-Power Serial Interface With Schmitt-Triggered Inputs

- On-Chip Output Buffer Amplifier With Rail-to-Rail

Operation

- Power-Down Capability

- Drop-In Compatible With DAC8531/01 and DAC8550 /51

- Temperature Range: -40°C to +105°C

- Available in a Tiny 8-Pin VSSOP Package

#### **3 Description**

The DAC8560 is a low-power, voltage output, 16-bit digital-to-analog converter (DAC). The DAC8560 includes a 2.5-V, 2-ppm/°C internal reference (enabled by default), giving a full-scale output voltage range of 0 V to 2.5 V. The internal reference has an initial accuracy of 0.02% and can source up to 20 mA at the V<sub>REF</sub> pin. The device is monotonic, provides very good linearity, and minimizes undesired code-to-code transient voltages (glitch). The DAC8560 uses a versatile 3-wire serial interface that operates at clock rates up to 30 MHz. It is compatible with standard SPI, QSPI, Microwire, and digital-signal-processor (DSP) interfaces.

The DAC8560 incorporates a power-on-reset (POR) circuit that ensures the DAC output powers up at zero scale and remains there until a valid code is written to the device. The DAC8560 contains a power-down feature, accessed over the serial interface, that reduces the current consumption of the device to 1.2  $\mu$ A at 5 V.

The low-power consumption, internal reference, and small footprint make this device ideal for portable, battery-operated equipment. The power consumption is 2.6 mW at 5 V, reducing to 6  $\mu$ W in power-down mode.

The DAC8560 is available in an 8-pin VSSOP package.

#### 7.3.1 Digital-to-Analog Converter (DAC)

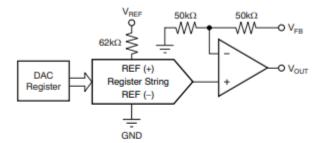

The DAC8560 architecture consists of a string DAC followed by an output buffer amplifier. Figure 63 shows a block diagram of the DAC architecture.

Figure 63. DAC8560 Architecture

The input coding to the DAC8560 is straight binary, so the ideal output voltage is given by:

$$V_{OUT} = \frac{D_{IN}}{65536} \times V_{REF}$$

where  $D_{IN}$  = decimal equivalent of the binary code that is loaded to the DAC register; it can range from 0 to 65535. (1)

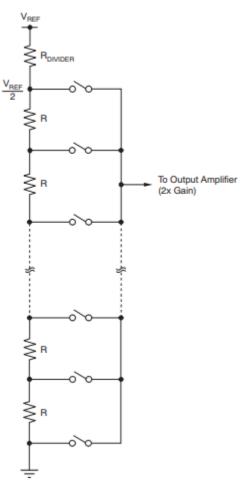

#### 7.3.2 Resistor String

The resistor string section is shown in Figure 64. It is simply a string of resistors, each of value R. The code loaded into the DAC register determines at which node on the string the voltage is tapped off to be fed into the output amplifier by closing one of the switches connecting the string to the amplifier. It is monotonic because it is a string of resistors.

Figure 64. Resistor String

#### 2 Applications

- Process Control

- Data Acquisition Systems

- Closed-Loop Servo-Control

INFORTANT NOTION

. ..

. . . . .

. . . . ..

- PC Peripherals

- Portable Instrumentation

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| DAC8560     | VSSOP (8) | 3.00 mm × 3.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

... .

. .

#### $V_{DD}$ V<sub>FB</sub> VREF C Ref (+) VOUT 16-Bit DAC ò 2.5V Reference 16 DAC Register 16 SYNC PWD Resistor Shift Register SCLK Control Network DIN GND

#### **Functional Block Diagram**

.

J

.. . ....

#### 6.5 Electrical Characteristics

\v\_{DD} = 2.7 V to 5.5 V, -40°C to +105°C range (unless otherwise noted)

| PARAMETER                         | TEST CONDITIONS                                                                                                    |                    | MIN              | ГҮР МАХ          | UNIT   |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------|------------------|------------------|--------|--|

| STATIC PERFORMANCE <sup>(1)</sup> |                                                                                                                    |                    | •                |                  |        |  |

| Resolution                        |                                                                                                                    |                    | 16               |                  | Bits   |  |

| Relative accuracy                 | Measured by line passing through                                                                                   | DAC8560A, DAC8560C |                  | ±4 ±12           | LSB    |  |

|                                   | codes 485 and 64714                                                                                                | DAC8560B, DAC8560D |                  | ±4 ±8            | LSB    |  |

| Differential nonlinearity         | 16-bit Monotonic                                                                                                   | :                  | ±0.5 ±1          | LSB              |        |  |

| Zero-code error                   |                                                                                                                    |                    | ±5 ±12           | mV               |        |  |

| Full-scale error                  | Measured by line passing through co                                                                                | :                  | ±0.2 ±0.5        | % of FSR         |        |  |

| Gain error                        | 7                                                                                                                  | ±                  | 0.05 ±0.2        | % of FSR         |        |  |

| Zero-code error drift             |                                                                                                                    | ±4                 | μV/°C            |                  |        |  |

| Gain temperature coefficient      | V <sub>DD</sub> = 5 V                                                                                              |                    |                  | ±1               | ppm of |  |

|                                   | V <sub>DD</sub> = 2.7 V                                                                                            |                    |                  | ±3               | FSR/°C |  |

| PSRR                              | Power supply rejection ratio                                                                                       | Output unloaded    |                  | 1                | mV/V   |  |

| OUTPUT CHARACTERISTIC             | S <sup>(2)</sup>                                                                                                   |                    | •                |                  |        |  |

| Output voltage range              |                                                                                                                    | 0                  | V <sub>REF</sub> | V                |        |  |

| Output voltage settling time      | To ±0.003% FSR, 0200h to FD00h, $R_L = 2 k\Omega$ ,<br>0 pF < $C_L < 200 pF$<br>$R_L = 2 k\Omega$ , $C_L = 500 pF$ |                    |                  | 8 10             | μs     |  |

|                                   |                                                                                                                    |                    |                  | 12               |        |  |

| Slew rate                         |                                                                                                                    | 1.8                | V/µs             |                  |        |  |

| One office to detail when         | $R_L = \infty$                                                                                                     |                    |                  | 470              | -5     |  |

| Capacitive load stability         | $R_L = 2 k\Omega$                                                                                                  |                    | 1                | 000              | pF     |  |

| Code change glitch impulse        | 1 LSB change around major carry                                                                                    | (                  | ).15             | nV-s             |        |  |

| Digital feedthrough               | SCLK toggling, SYNC high                                                                                           | (                  | 0.15             | nV-s             |        |  |

| DC output impedance               | At mid-code input                                                                                                  |                    | 1                | Ω                |        |  |

| Short-circuit current             | V <sub>DD</sub> = 5 V                                                                                              |                    |                  | 50               | mA     |  |

|                                   | V <sub>DD</sub> = 3 V                                                                                              |                    |                  | 20               |        |  |

| Devuen um time e                  | Coming out of power-down mode V <sub>DD</sub> = 5 V                                                                |                    |                  | 2.5              | μs     |  |

| Power-up time                     | Coming out of power-down mode V <sub>DD</sub> = 3 V                                                                |                    |                  | 5                |        |  |

| AC PERFORMANCE <sup>(2)</sup>     | ·                                                                                                                  |                    | •                |                  | •      |  |

| SNR                               |                                                                                                                    |                    | 88               | dB               |        |  |

| THD                               | T <sub>A</sub> = 25°C, BW = 20 kHz, V <sub>DD</sub> = 5 V.                                                         |                    | -77              | dB               |        |  |

| SFDR                              | T <sub>A</sub> = 25°C, BW = 20 kHz, $V_{DD}$ = 5 V,<br>1st 19 harmonics removed for SNR c                          |                    | 79               | dB               |        |  |

| SINAD                             | 7                                                                                                                  |                    | 77               | dB               |        |  |

| DAC output noise density          | $T_A = 25^{\circ}C$ , at mid-code input, $f_{OUT} = 1$                                                             |                    | 170              | nV/√Hz           |        |  |

| DAC output noise                  | T <sub>A</sub> = 25°C, at mid-code input, 0.1 Hz                                                                   |                    | 50               | μV <sub>PP</sub> |        |  |

(1) Linearity calculated using a reduced code range of 485 to 64714; output unloaded.

(2) Ensured by design and characterization, not production tested.

### The DAC 8560

What is the INL performance of this DAC?

ENOB?

What is the spectral performance?

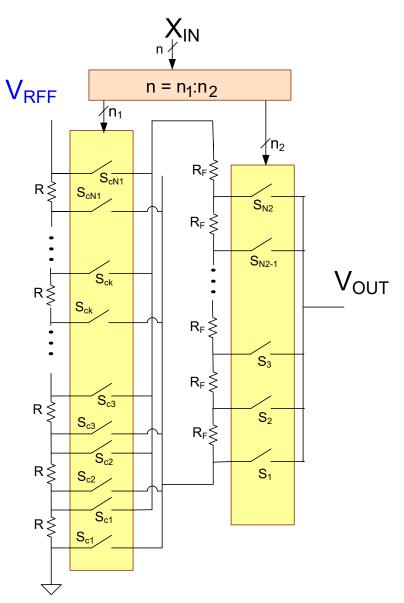

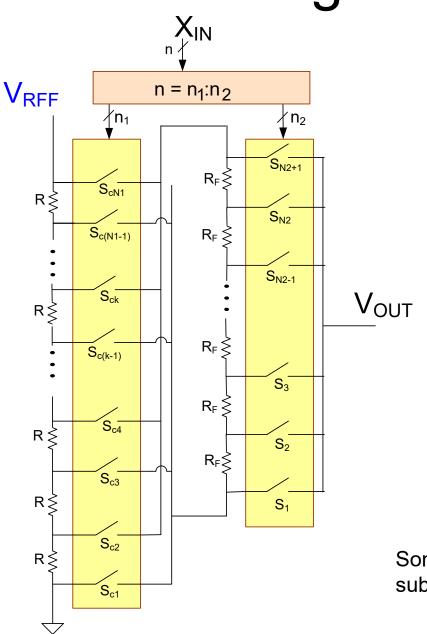

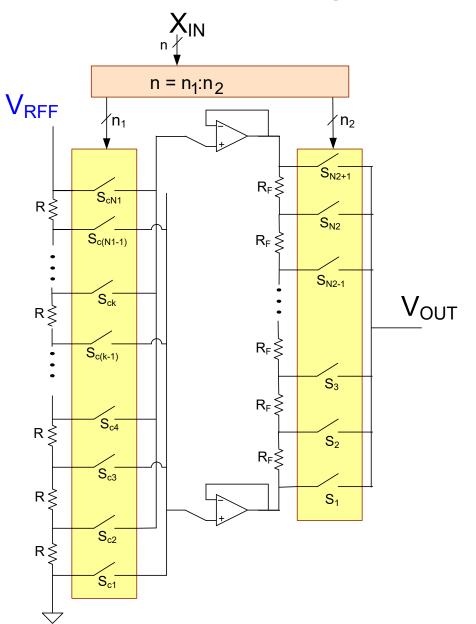

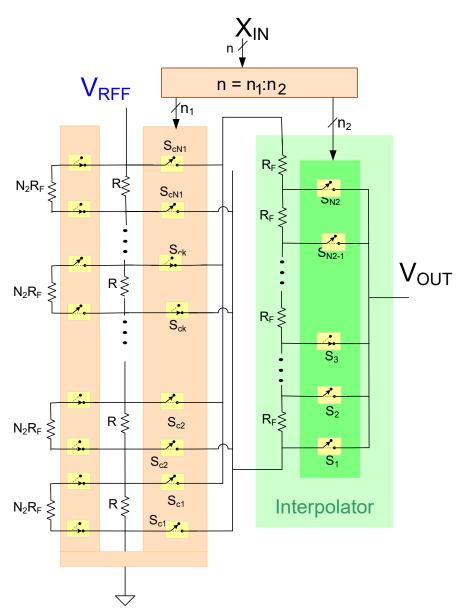

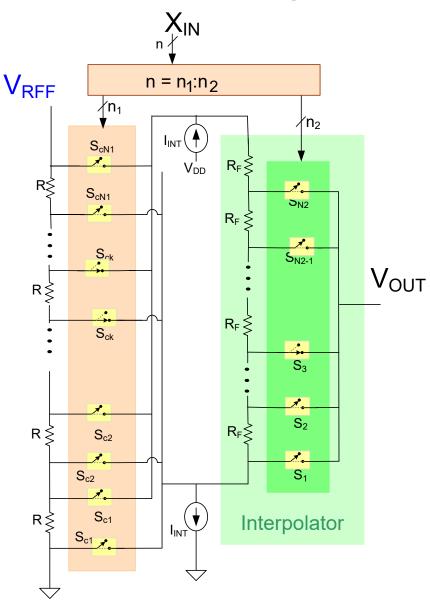

Sometimes termed sub-divider, sub-range or dual-string DAC

# Stay Safe and Stay Healthy !

### End of Lecture 32